# CTI 2500 Series Controller PROGRAMMING REFERENCE MANUAL

Version 1.29

CTI Part # 062-00371

# Copyright 2009-2019 Control Technology Inc. All rights reserved.

This manual is published by Control Technology Inc., 5734 Middlebrook Pike, Knoxville TN 37921. This manual contains references to brand and product names which are trade names, trademarks, and/or registered trademarks of Control Technology Inc.

Siemens®, SIMATIC®, and Series 505® are registered trademarks of Siemens AG and Siemens Energy and Automation, Inc.

TISOFT™ and PowerMath™ are trademarks of Siemens Energy and Automation. Inc.

PLC WorkShop® is a registered trademark of FasTrak Softworks, Inc.

Other references to brand and product names are trade names, trademarks, and/or registered trademarks of their respective holders.

#### **DOCUMENT DISCLAIMER STATEMENT**

Every effort has been made to ensure the accuracy of this document; however, errors do occasionally occur. CTI provides this document on an "as is" basis and assumes no responsibility for direct or consequential damages resulting from the use of this document. This document is provided without express or implied warranty of any kind, including but not limited to the warranties of merchantability or fitness for a particular purpose. This document and the products it references are subject to change without notice. If you have a comment or discover an error, please call us toll free at 1-800-537-8398 or email us at sales @controltechnology.com.

|          |           | REVISION HISTORY                                                                                                                         |

|----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| V1.0     | 10/14/08  | Original Version                                                                                                                         |

| V1.1     | 10/16/08  | Corrected typos                                                                                                                          |

| V1.2     | 10/30/08  | Added description to PRINT instruction                                                                                                   |

|          |           | Made corrections to SMC instruction                                                                                                      |

|          |           | Corrected description of PRINT status bits in STW191                                                                                     |

| V1.3     | 1/19/09   | Added table to define addresses for non-retentive and retentive relays.                                                                  |

| V1.4     | 5/19/09   | Added descriptions to Analog (PID) Loop parameter fields.                                                                                |

|          |           | Added table for Special Function Error Codes                                                                                             |

| V1.5     | 7/29/09   | Added descriptions for new SF instructions and SF Subroutine features                                                                    |

|          |           | These features are supported in 2500 Series CPU firmware V6.0 (or later)                                                                 |

|          |           | and 505 WorkShop V4.50 (or later).                                                                                                       |

| V1.6     | 8/27/09   | Corrected description of SF SWITCH / CASE / ENDSWITCH instruction.                                                                       |

| V1.7     | 9/14/09   | Corrected description of RLL Table to Word (TTOW) and Word to Table                                                                      |

|          |           | (WTOT) instructions.                                                                                                                     |

|          |           | Enhanced description and added example for SFSUB0 instruction.                                                                           |

| V1.8     | 6/13/10   | Added instructions for run-time edit.                                                                                                    |

|          |           | Updated copyright date.                                                                                                                  |

| 1/4.0    | 0/00/40   | Updated Status Word table.                                                                                                               |

| V1.9     | 6/29/10   | Added description and figure of bit numbering within words to Data                                                                       |

|          |           | Representation section.                                                                                                                  |

|          |           | Enhanced description for Run-Time RLL Edits. Corrected description in Conditional Branching (IF-ENDIF) example                           |

|          |           | Added description of differences between CTI 2500 Series PLC and                                                                         |

|          |           | SIMATIC 505 controllers regarding operation of Cyclic SF Programs.                                                                       |

| V1.10    | 8/16/10   | Corrected description of errors reported by PRINT instruction.                                                                           |

| V1.10    | 11/3/10   | Greatly enhanced the descriptions of the Analog Alarm and Analog (PID)                                                                   |

| V 1. 1 1 | 11/3/10   | Loop operation and parameter set.                                                                                                        |

| V1.12    | 12/10/10  | Enhanced description for RSD instruction.                                                                                                |

| V 1.12   | 12/10/10  | Enhanced description of the SF SSR instruction and corrected example.                                                                    |

| V1.13    | 12/20/10  | Corrected Alarm Flag tables in Section 4.3 and Appendix B.                                                                               |

| V1.14    | 09/19/11  | Added operational notes for Loop PV Range Parameters (Section 5.3.6)                                                                     |

|          |           | and Remote I/O Errors (STW145-146 in Appendix A).                                                                                        |

|          |           | Corrected typos.                                                                                                                         |

| V1.15    | 1/11/12   | Added descriptions for new RLL instructions (ONDC, OFDC, MEDRM) and                                                                      |

|          |           | enhanced features for Relational/Comparison instructions (EQU, NEQ,                                                                      |

|          |           | LESS, LEQ, GRT, GEQ).                                                                                                                    |

|          |           | These features are supported in 2500 Series CPU firmware V6.18 (or later)                                                                |

|          |           | and 505 WorkShop V4.60 (or later).                                                                                                       |

| V1.16    | 8/14/13   | Added descriptions for Special Function MATH operations:                                                                                 |

|          |           | Exponentiation and Logarithm                                                                                                             |

| V1.17    | 11/20/13  | Corrected typo in Alarm Deadband example. (Section 4.2.14).                                                                              |

|          |           | Corrected description in Loop Deviation Alarm Limits (Section 5.3.31) and                                                                |

| 1/4 40   | 0/4 4/4 4 | Analog Deviation Alarms (Section 5.2.16).                                                                                                |

| V1.18    | 3/14/14   | Corrected description of STW231 in PLC Status Words (Appendix A).                                                                        |

| \/4.40   | E/07/4.4  | Added description for Profibus I/O Status Bit 6 (added in firmware V6.11).                                                               |

| V1.19    | 5/27/14   | Corrected description of operation for CTR instruction to document special                                                               |

| \/1.20   | 1/18/16   | case when TCC and TCP are both set to zero.                                                                                              |

| V1.20    | 1/18/16   | Added statement regarding SF Program Size limitation of 32767 bytes                                                                      |

| V1.21    | 4/12/16   | maximum for each SFPGM and SFSUB (Section 3.4.1).                                                                                        |

| V I.∠ I  | 4/12/10   | Corrected description of SF Program operation when configured to be called as part of the Analog (PID) Loop operation (Section 3.2.1.3). |

| V1.22    | 6/6/16    | Improved description of PACKRS instruction (Section 3.2.1.3).                                                                            |

| v 1.ZZ   | 0/0/10    | Improved description of FACKINS instruction (Section 3.3.10)                                                                             |

| REVISION HISTORY |          |                                                                                                                                                                                                                                                                                           |  |

|------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

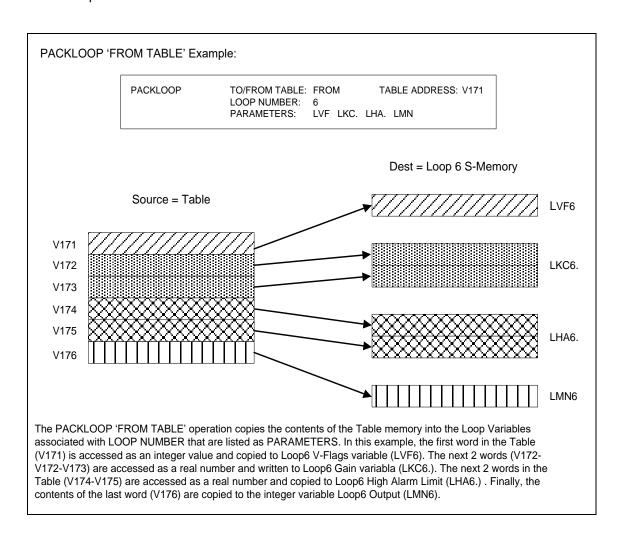

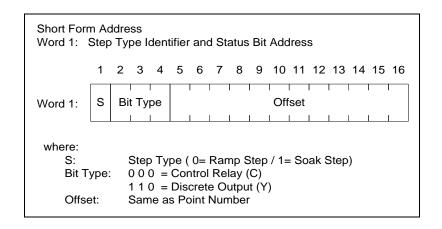

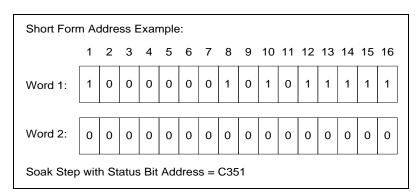

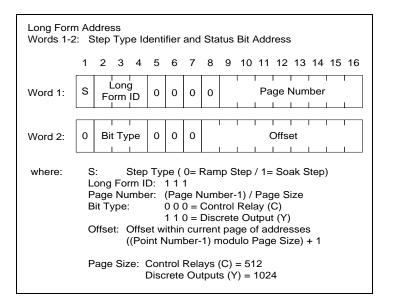

|                  |          | Added details on difference between CTI 2500 Series CPU and SIMATIC® 505 controller when using PACKRS 'FROM TABLE' operation. Enhanced description for use of Short/Long Form Address formats used to specify Memory Type and Offset of Ramp/Soak step status bits.                       |  |

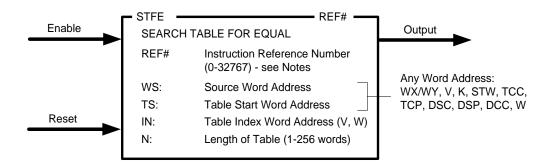

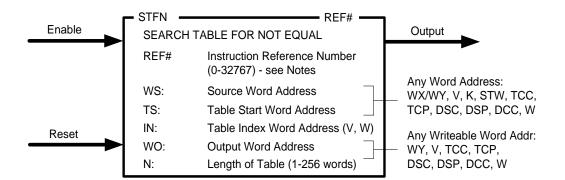

| V1.23            | 6/9/16   | Improved operational descriptions for Search Table For Equal (Section 2.6.10) and Search Table For Not Equal (Section 2.6.11) instructions.                                                                                                                                               |  |

| V1.24            | 8/18/16  | Corrected description of SF Program execution queues (limit of 32 active programs applies only to Cyclic SFPGMs (Section 2.11.12).  Added description for compilation of SF Programs and SF Subroutines with recommendations and procedures for on-line SF Program edits (Section 3.2.3). |  |

| V1.25            | 9/15/16  | Corrected descriptions for RLL instructions: STFE (Section 2.6.10) and STFN (Section 2.6.11). Corrected memory tables in Sections 3.5.16-17, 3.6 and Appendix B. Added 'Table of Contents' hyperlinks and Bookmarks to the PDF document.                                                  |  |

| V1.26            | 11/29/16 | Enhanced description of Special Function MATH statement (Section 3.4.18). Corrected various typos, document 'Properties' information, and PDF options to correct Font formatting issues.                                                                                                  |  |

| V1.27            | 11/30/18 | Added description for Data Cache Connection Status (STW267) in Appendix A – PLC STATUS WORDS.                                                                                                                                                                                             |  |

| V1.28            | 2/14/19  | Corrected descriptions for STW258-259 (Serial Number) and STW267 (Data Cache Connection Status) added detailed descriptions for STW262-454 in Appendix A – PLC STATUS WORDS.                                                                                                              |  |

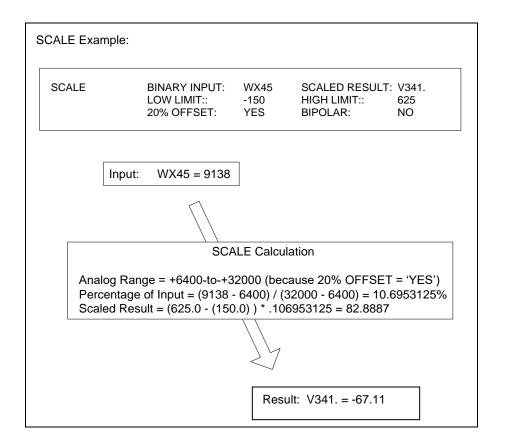

| V1.29            | 8/4/20   | Corrected SCALE example in section 3.5.22. Incorrectly showed result as V341. = 82.8887. The correct value is -67.11.                                                                                                                                                                     |  |

# **PREFACE**

This **Programming Reference Manual** provides reference information for the CTI 2500 Controller. The information in this manual is directed to individuals who will be developing user programs for the controller.

For information regarding the product features, installation, and operation, you should also obtain the *CTI 2500 Installation and Operation Guide (CTI Part #* 062 -00370). This manual may be downloaded from the CTI Web site http://www.controltechnology.com/support/manuals/.

# **USAGE CONVENTIONS**

#### Note:

Notes alert the user to special features or procedures.

### **CAUTION**

Cautions alert the user to procedures that could damage equipment.

### **WARNING:**

Warnings alert the user to procedures that could damage equipment and endanger the user.

# **TABLE OF CONTENTS**

| CHAPTE         | R 1 OVERVIEW                                         | 1  |

|----------------|------------------------------------------------------|----|

| 1.1            | Introduction                                         | 1  |

| 1.2            | PROGRAMMING OVERVIEW                                 | 1  |

| 1.2.1          |                                                      |    |

| 1.2.2          |                                                      |    |

| 1.2.3          |                                                      |    |

| 1.2.4          | Analog Loops                                         | 3  |

| 1.3            | CONTROLLER DATA TYPES                                | 4  |

| 1.4            | DATA REPRESENTATION                                  | 6  |

| 1.5            | RUN-TIME RLL EDITS                                   | 8  |

| 1.5.1          | Syntax Checking                                      |    |

| 1.5.2          |                                                      |    |

| 1.5.3          | Additional Considerations                            | 10 |

| CHAPTE         | R 2 RELAY LADDER LOGIC                               | 13 |

| 2.1            | Overview                                             | 13 |

|                | RLL INSTRUCTION SUMMARY                              |    |

| 2.2.1          |                                                      |    |

| 2.2.2          |                                                      |    |

| 2.2.3          |                                                      |    |

| 2.2.4          |                                                      |    |

| 2.2.5          |                                                      |    |

| 2.2.6          | <b>5</b> 1                                           |    |

| 2.2.7          |                                                      |    |

| 2.2.8          | J 1                                                  |    |

| 2.2.9          | '                                                    |    |

|                | RLL MEMORY ACCESS                                    |    |

|                | RELAY INSTRUCTIONS                                   |    |

| 2.4.1          | Open Contact                                         |    |

| 2.4.2          |                                                      |    |

| 2.4.3<br>2.4.4 | <b>5</b>                                             |    |

| 2.4.4          |                                                      |    |

| 2.4.6          |                                                      |    |

| 2.4.7          |                                                      |    |

| 2.4.8          |                                                      |    |

| 2.4.9          |                                                      |    |

| 2.4.1          | 0 Immediate Closed Contact                           | 29 |

| 2.4.1          | 1 Immediate Coil                                     | 29 |

| 2.4.1          |                                                      |    |

| 2.4.1          |                                                      |    |

| 2.4.1          |                                                      |    |

|                | ELECTRO-MECHANICAL INSTRUCTIONS (TIMER/COUNTER/DRUM) |    |

| 2.5.1          |                                                      |    |

| 2.5.2          | Up-Down Counter (UDC)                                | 33 |

| 2.5.3<br>2.5.4  | On-Delay Timer (TMR / TMRF)                       |     |

|-----------------|---------------------------------------------------|-----|

| 2.5.5           | Motor Control Alarm Timer (MCAT)                  | 39  |

| 2.5.6           | On-Delay Coil (ONDC)                              |     |

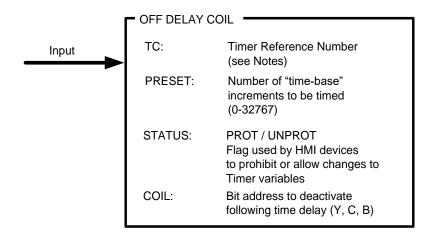

| 2.5.7           | Off-Delay Coil (OFFDC)                            |     |

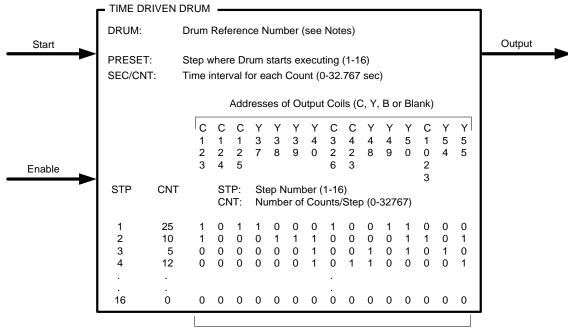

| 2.5.8           | DRUM (Time-Based)                                 | 47  |

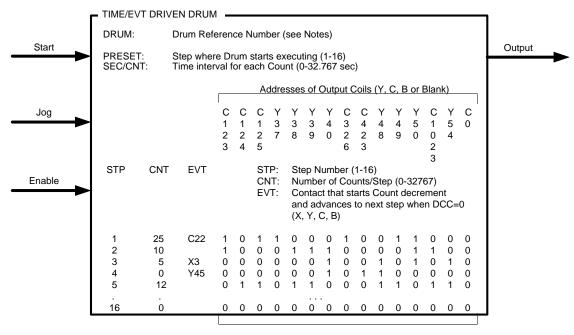

| 2.5.9           | Time/Event DRUM (EDRUM)                           |     |

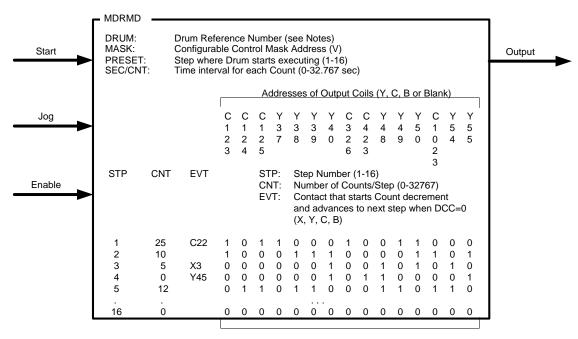

| 2.5.10          | Maskable Event Drum with Discrete Outputs (MDRMD) | 52  |

| 2.5.11          | Maskable Event Drum with Word Output (MDRMW)      | 56  |

| 2.5.12          | Mega Event DRUM (MEDRM)                           | 60  |

| 2.6 REI         | LATIONAL / COMPARISON OPERATIONS                  | 67  |

| 2.6.1           | Compare (CMP)                                     |     |

| 2.6.2           | Equal (EQU)                                       |     |

| 2.6.3           | Greater or Equal (GEQ)                            |     |

| 2.6.4           | Greater (GTR)                                     |     |

| 2.6.5           | Less or Equal (LEQ)                               |     |

| 2.6.6           | Less (LESS)                                       |     |

| 2.6.7           | Not Equal (NEQ)                                   |     |

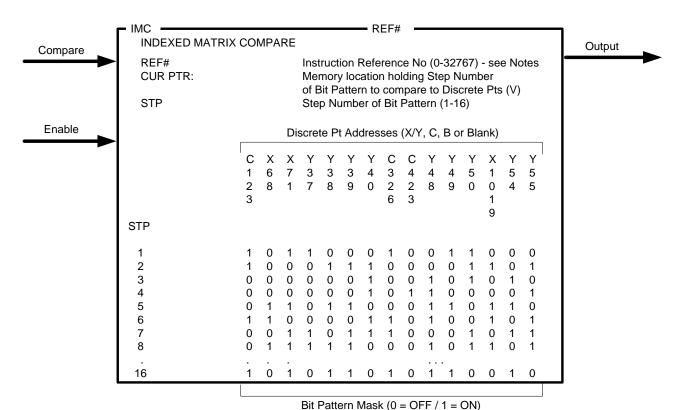

| 2.6.8           | Indexed Matrix Compare (IMC)                      |     |

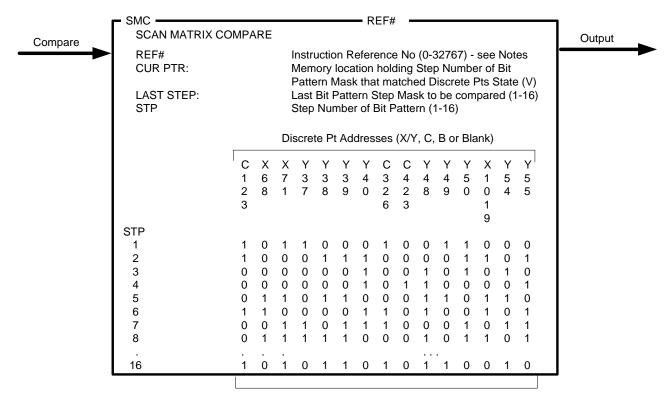

| 2.6.9           | Scan Matrix Compare (SMC)                         |     |

| 2.6.10          | Search Table For Equal (STFE)                     |     |

| 2.6.10          | Search Table For Not Equal (STFN)                 |     |

|                 | . , ,                                             |     |

|                 | OPERATIONS                                        |     |

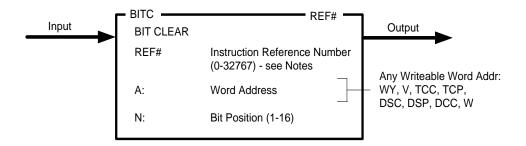

| 2.7.1           | Bit Clear (BITC)                                  |     |

| 2.7.2           | Bit Set (BITS)                                    |     |

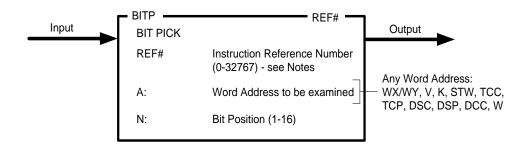

| 2.7.3           | Bit Pick (BITP)                                   |     |

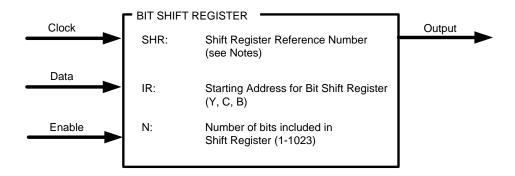

| 2.7.4           | Bit Shift Register (SHRB)                         |     |

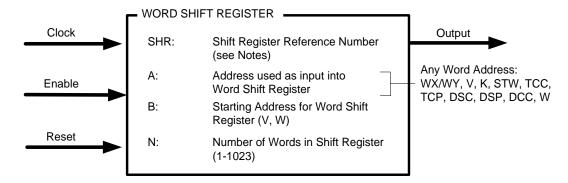

| 2.7.5           | Word Shift Register (SHRW)                        |     |

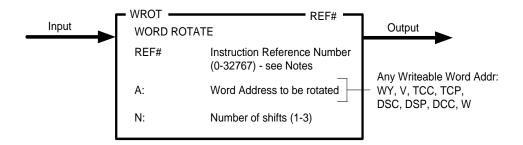

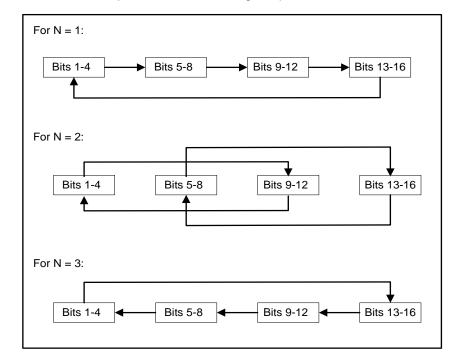

| 2.7.6           | Word Rotate (WROT)                                |     |

| 2.8 MA          | TH / LOGIC OPERATIONS                             | 97  |

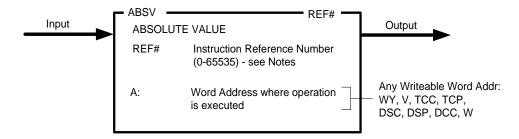

| 2.8.1           | Absolute Value (ABSV)                             | 97  |

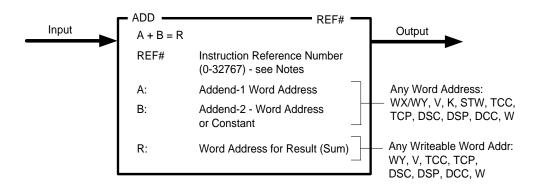

| 2.8.2           | Addition (ADD)                                    | 98  |

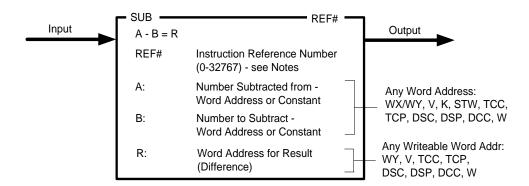

| 2.8.3           | Subtraction (SUB)                                 | 99  |

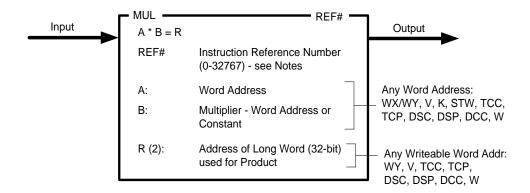

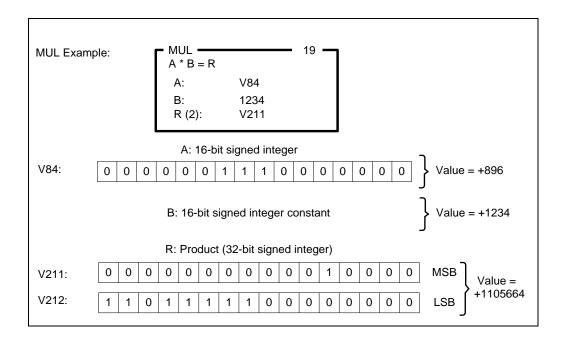

| 2.8.4           | Multiplication (MUL)                              | 100 |

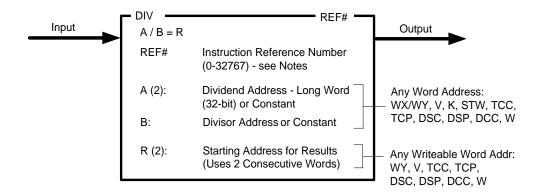

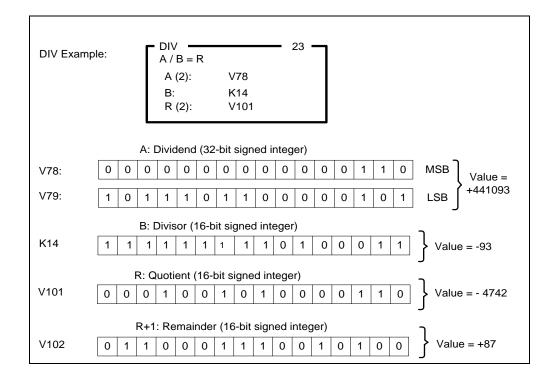

| 2.8.5           | Division (DIV)                                    | 102 |

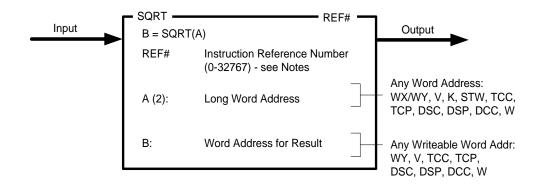

| 2.8.6           | Square Root (SQRT)                                |     |

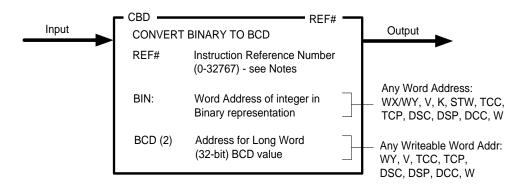

| 2.8.7           | Binary to BCD Conversion (CBD)                    |     |

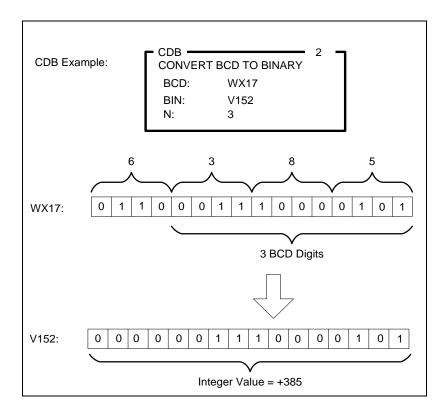

| 2.8.8           | BCD to Binary Conversion (CDB)                    |     |

| 2.9 Lo          | GIC OPERATIONS                                    | 110 |

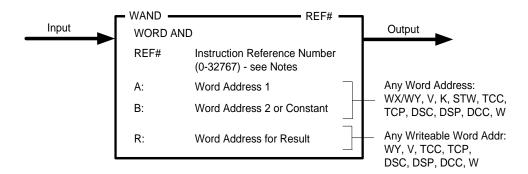

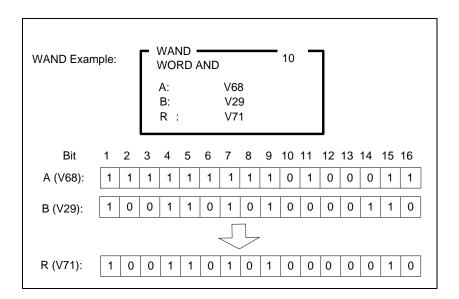

| 2.9.1           | Word AND (WAND)                                   |     |

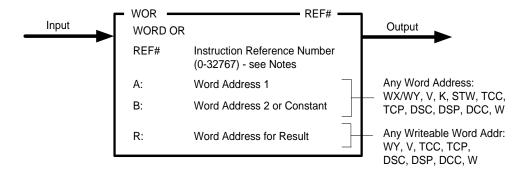

| 2.9.2           | Word OR (WOR)                                     |     |

| 2.9.3           | Word Exclusive-OR (WXOR)                          |     |

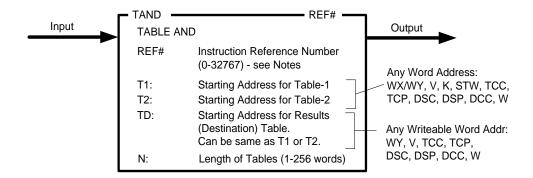

| 2.9.4           | Table AND (TAND)                                  |     |

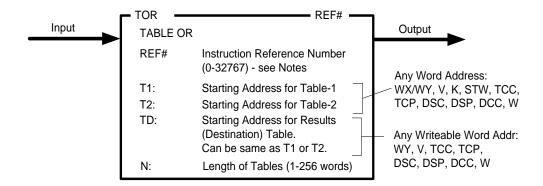

| 2.9.5           | Table OR (TOR)                                    |     |

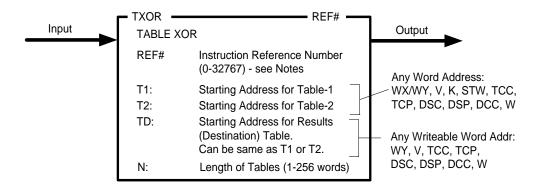

| 2.9.6           | Table Exclusive-OR (TXOR)                         |     |

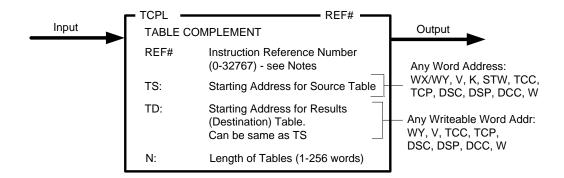

| 2.9.7           | Table Complement (TCPL)                           |     |

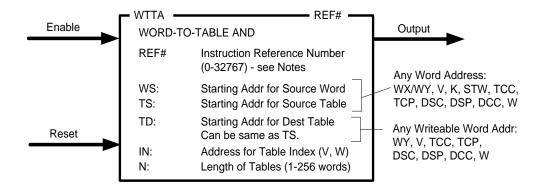

| 2.9.7           | Word-to-Table AND (WTTA)                          |     |

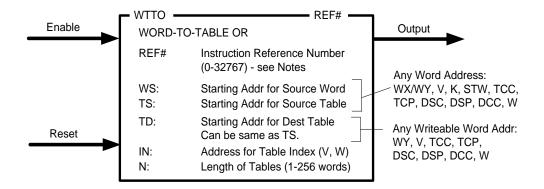

| 2.9.6           | Word-to-Table OR (WTTO)                           |     |

| 2.9.9<br>2.9.10 | Word-to-Table OR (WTTO)                           |     |

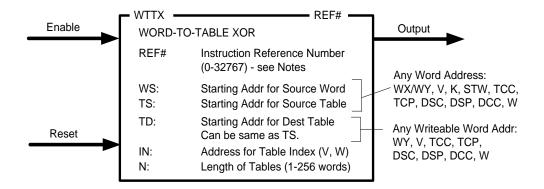

|                 | · · · · ·                                         |     |

|                 | ORD / TABLE MOVE OPERATIONS                       |     |

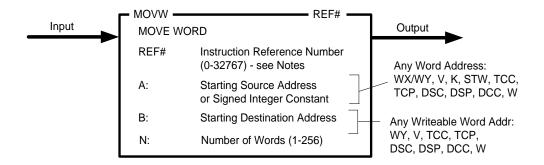

| 2.10.1          | Move Word (MOVW)                                  |     |

| 2.10.2          | Move with Index (MWI)                             | 131 |

| 2.10.3  | Move Word From Table (MWFT)                   | 133 |

|---------|-----------------------------------------------|-----|

| 2.10.4  | Move Word To Table (MWTT)                     |     |

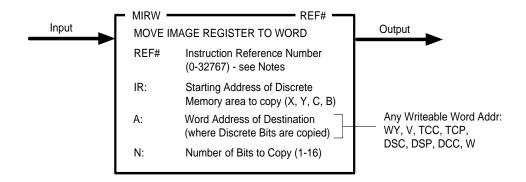

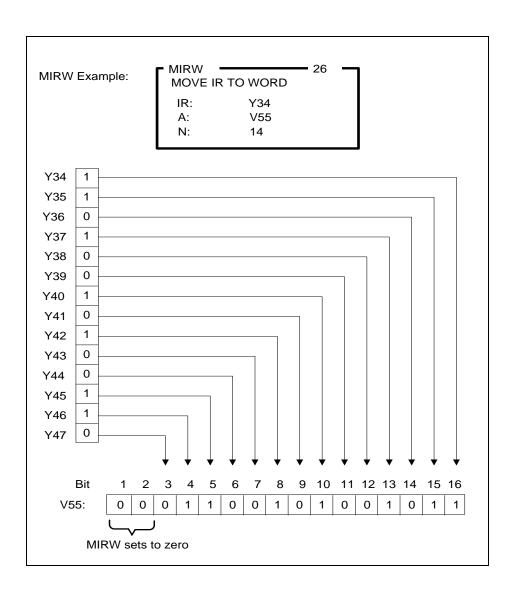

| 2.10.5  | Move Image Register to Word (MIRW)            | 137 |

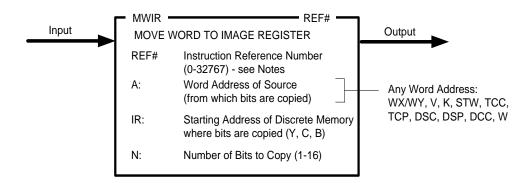

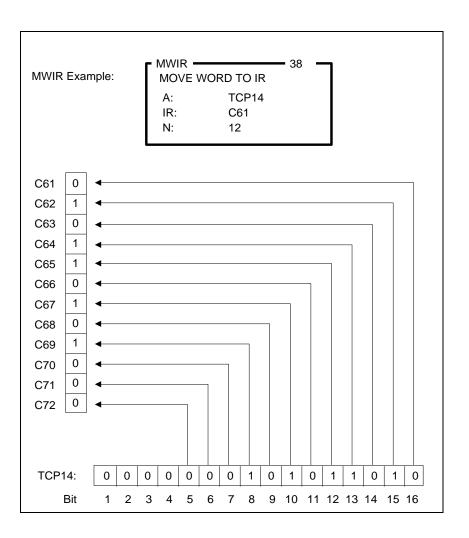

| 2.10.6  | Move Word to Image Register (MWIR)            | 139 |

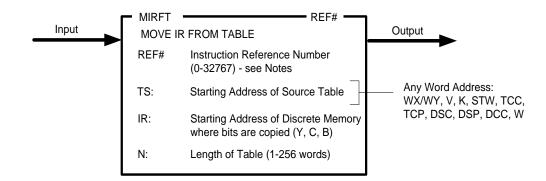

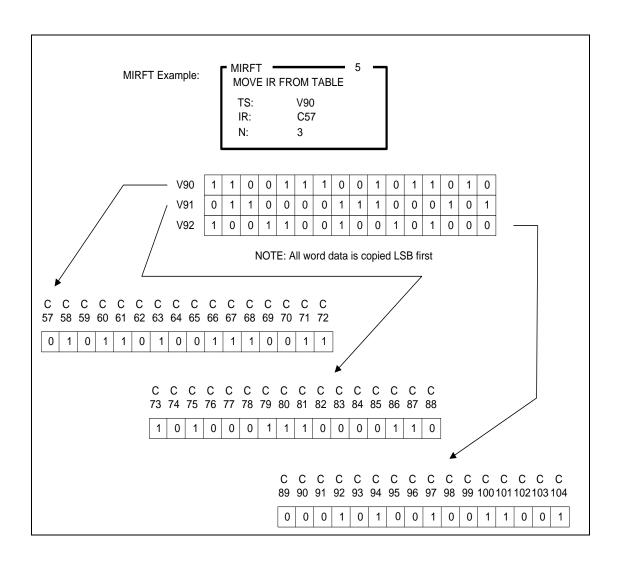

| 2.10.7  | Move Image Register From Table (MIRFT)        | 141 |

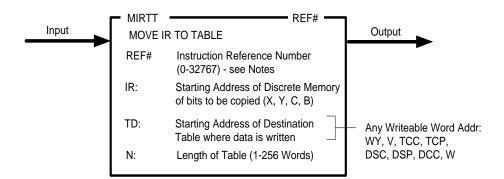

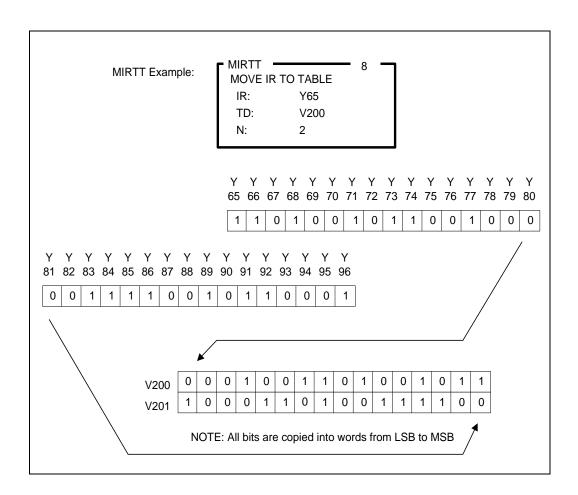

| 2.10.8  | Move Image Register To Table (MIRTT)          |     |

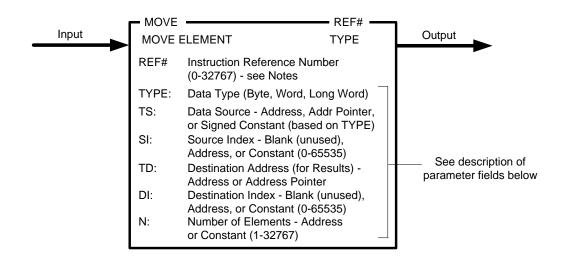

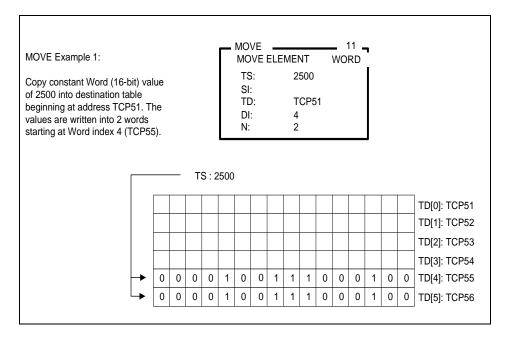

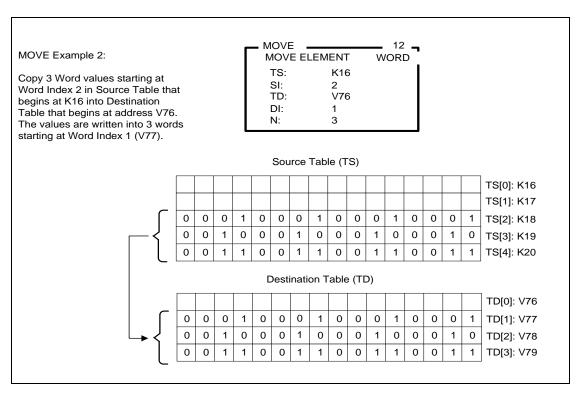

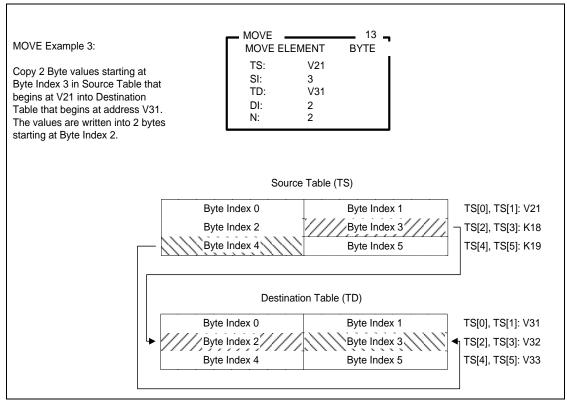

| 2.10.9  | Move Element (MOVE)                           |     |

| 2.10.10 | · · · · · · · · · · · · · · · · · · ·         |     |

| 2.10.11 |                                               |     |

| 211 Pr  | ROGRAM CONTROL OPERATIONS                     |     |

| 2.11.1  | Unconditional END (END)                       |     |

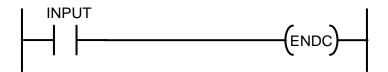

| 2.11.2  | Conditional END (ENDC)                        |     |

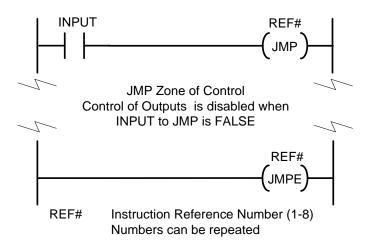

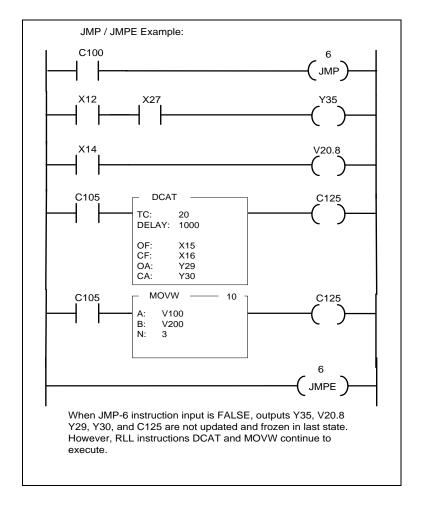

| 2.11.3  | Jump (JMP) / Jump End (JMPE)                  | 156 |

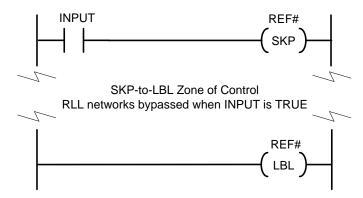

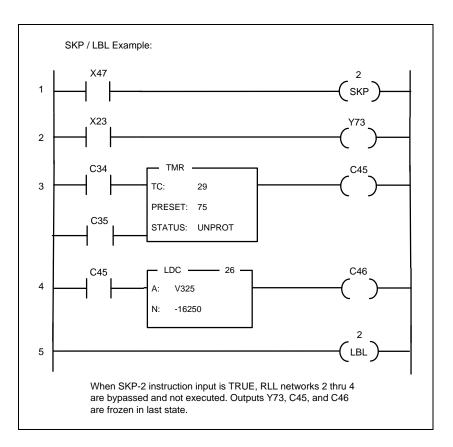

| 2.11.4  | Skip (SKP) / Label (LBL)                      |     |

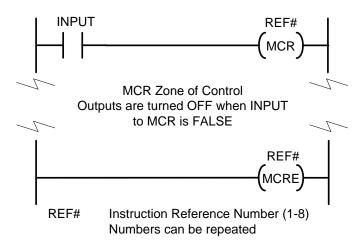

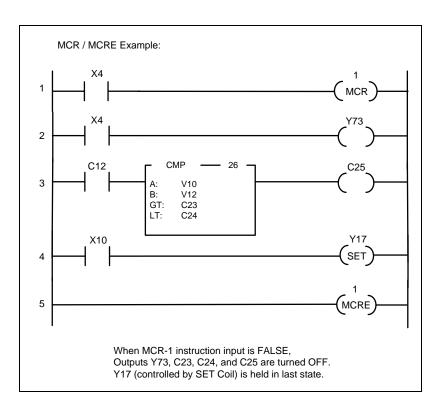

| 2.11.5  | Master Control Relay (MCR) / MCR End (MCRE)   | 161 |

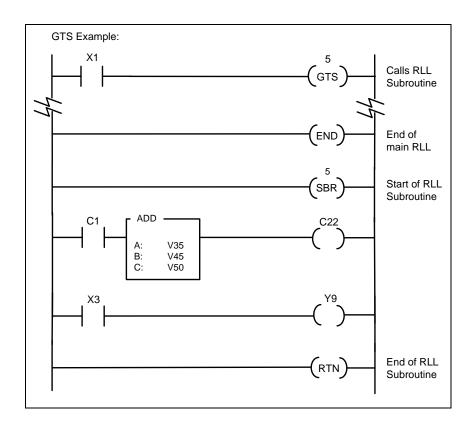

| 2.11.6  | Go To Subroutine (GTS)                        |     |

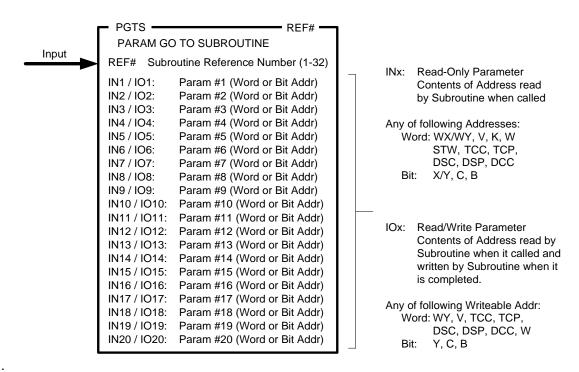

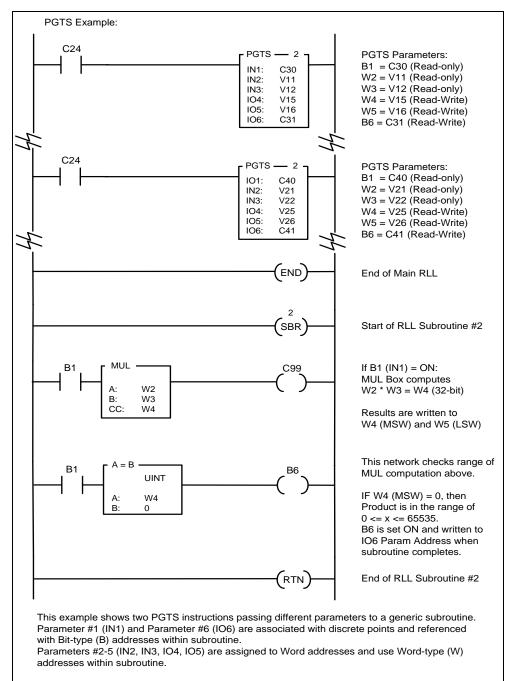

| 2.11.7  | Parameterized Go To Subroutine (PGTS)         | 166 |

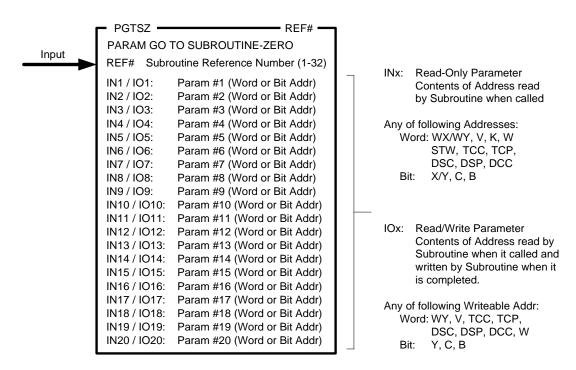

| 2.11.8  | Parameterized Go To Subroutine – Zero (PGTSZ) | 170 |

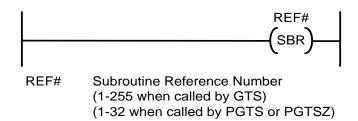

| 2.11.9  | Start of Subroutine (SBR)                     |     |

| 2.11.10 | · · ·                                         |     |

| 2.11.11 | ,                                             |     |

| 2.11.12 |                                               |     |

| 2.11.13 |                                               |     |

| 2.11.14 | ( )                                           |     |

| 2.11.15 |                                               |     |

| 2.11.16 |                                               |     |

| 2.11.17 |                                               |     |

| 2.11.18 | ` ,                                           |     |

| 2.11.19 | · · · ·                                       |     |

| 2.11.20 | . , ,                                         |     |

| 2.11.21 | ,                                             |     |

| 2.11.22 | . , ,                                         |     |

| 2.11.23 |                                               |     |

| 2.11.24 |                                               |     |

| 2.11.25 | No Operation (NOP)                            | 211 |

| CHAPTER | 3 SF PROGRAMS AND SUBROUTINES                 | 213 |

| 3.1 O   | VERVIEW                                       | 213 |

|         | F PROGRAM/SUBROUTINE EXECUTION                |     |

| 3.2.1   | SF Programs                                   |     |

| 3.2.2   | SF Subroutines                                |     |

| 3.2.3   | Editing of SF Programs during Run Mode        |     |

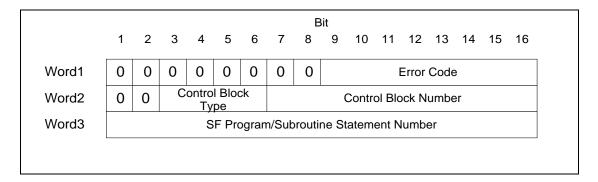

|         | PECIAL FUNCTION ERROR REPORTING AND RESPONSE  |     |

|         |                                               |     |

|         | PECIAL FUNCTION MEMORY USAGE                  |     |

| 3.4.1   | SF Program Size                               |     |

| 3.4.2   | SF Local Memory                               |     |

| 3.4.3   | Memory Array Indexing                         |     |

|         | PECIAL FUNCTION INSTRUCTIONS                  |     |

| 3.5.1   | SF Instruction Data Fields                    |     |

| 3.5.2   | Comment (*)                                   |     |

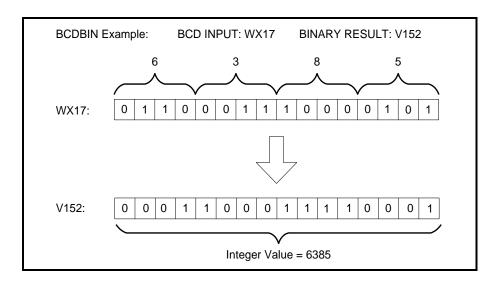

| 3.5.3   | BCD-to-Binary Conversion (BCDBIN)             |     |

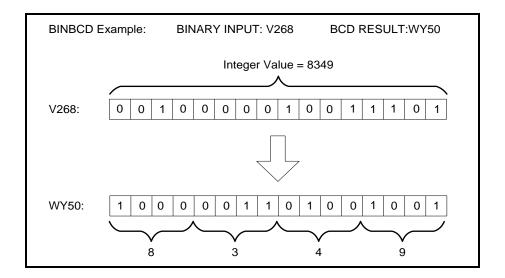

| 3.5.4   | Binary-to-BCD Conversion (BINBCD)             |     |

| 3.5.5                                                                                                                                     | Call SF Subroutine (CALL)                                                                                                                                                                                                      |                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

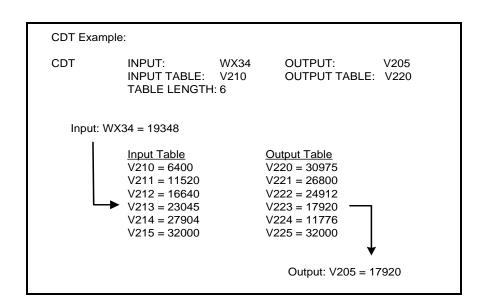

| 3.5.6                                                                                                                                     | Correlated Data Table (CDT)                                                                                                                                                                                                    | 235                                             |

| 3.5.7                                                                                                                                     | Exit on Error (EXIT)                                                                                                                                                                                                           |                                                 |

| 3.5.8                                                                                                                                     | Fall Through Shift Register (FTSR-IN / FTSR-OUT)                                                                                                                                                                               | 238                                             |

| 3.5.9                                                                                                                                     | Conditional Looping - FOR / NEXT                                                                                                                                                                                               |                                                 |

| 3.5.10                                                                                                                                    | Unconditional Branching - GOTO / LABEL                                                                                                                                                                                         |                                                 |

| 3.5.11                                                                                                                                    | Conditional Branching - IF (IIF) / ELSE / ENDIF                                                                                                                                                                                |                                                 |

| 3.5.12                                                                                                                                    | Integer Math Operations (IMATH)                                                                                                                                                                                                |                                                 |

| 3.5.13                                                                                                                                    | Lead/Lag Compensation (LEAD/LAG)                                                                                                                                                                                               |                                                 |

| 3.5.14                                                                                                                                    | Real Number Math Operations (MATH)                                                                                                                                                                                             |                                                 |

| 3.5.15                                                                                                                                    | Pack Data (PACK)                                                                                                                                                                                                               |                                                 |

| 3.5.16                                                                                                                                    | Pack Analog Alarm Data (PACKAA)                                                                                                                                                                                                |                                                 |

| 3.5.17                                                                                                                                    | Pack Loop Data (PACKLOOP)                                                                                                                                                                                                      |                                                 |

| 3.5.18                                                                                                                                    | Pack Ramp/Soak Data (PACKRS)                                                                                                                                                                                                   |                                                 |

| 3.5.19                                                                                                                                    | Pet Scan Watchdog (PETWD)                                                                                                                                                                                                      |                                                 |

| 3.5.20                                                                                                                                    | Print Message (PRINT)                                                                                                                                                                                                          |                                                 |

| 3.5.21                                                                                                                                    | Return from SF Program / Subroutine (RETURN)                                                                                                                                                                                   | 280                                             |

| 3.5.22                                                                                                                                    | Scale Analog Input to Engineering Units (SCALE)                                                                                                                                                                                |                                                 |

| 3.5.23                                                                                                                                    | Sequential Data Table (SDT)                                                                                                                                                                                                    |                                                 |

| 3.5.24                                                                                                                                    | Conditional Branching – SWITCH / CASE / ENDSWITCH                                                                                                                                                                              | 285                                             |

| 3.5.25                                                                                                                                    | Synchronous Shift Register (SSR)                                                                                                                                                                                               |                                                 |

| 3.5.26                                                                                                                                    | Scale Engineering Units to Analog Output (UNSCALE)                                                                                                                                                                             |                                                 |

| 3.5.27                                                                                                                                    | Conditional Looping - WHILE / ENDWHILE                                                                                                                                                                                         | 292                                             |

| 3.6 SI                                                                                                                                    | F PROGRAM/SUBROUTINE DATA VARIABLES                                                                                                                                                                                            |                                                 |

|                                                                                                                                           | F PROGRAM/SUBROUTINE ERROR CODES                                                                                                                                                                                               |                                                 |

| 3. <i>1</i> 31                                                                                                                            | - PROGRAM/SUBROUTINE ERROR CODES                                                                                                                                                                                               | 297                                             |

|                                                                                                                                           |                                                                                                                                                                                                                                |                                                 |

| CHARTER                                                                                                                                   | 4 ANALOG ALARMS                                                                                                                                                                                                                | 200                                             |

| CHAPTER                                                                                                                                   |                                                                                                                                                                                                                                |                                                 |

| _                                                                                                                                         | 4 ANALOG ALARMS                                                                                                                                                                                                                |                                                 |

| 4.1 O                                                                                                                                     | VERVIEW                                                                                                                                                                                                                        | 299                                             |

| 4.1 O                                                                                                                                     | VERVIEW                                                                                                                                                                                                                        | 299<br>299                                      |

| 4.1 O                                                                                                                                     | VERVIEWARM PARAMETERSAlarm Title                                                                                                                                                                                               | 299<br>299<br>300                               |

| 4.1 O<br>4.2 At<br>4.2.1                                                                                                                  | VERVIEWARM PARAMETERSARM PittleARM V-Flag Address                                                                                                                                                                              | 299<br>299<br>300<br>300                        |

| 4.1 O<br>4.2 At<br>4.2.1<br>4.2.2                                                                                                         | VERVIEW  _ARM PARAMETERS  Alarm Title  Alarm V-Flag Address  Sample Rate                                                                                                                                                       |                                                 |

| 4.1 O'<br>4.2 Al<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                                                                                      | VERVIEWARM PARAMETERSAlarm TitleAlarm V-Flag AddressSample RateProcess Variable Address (V, WX, WY, None)                                                                                                                      |                                                 |

| 4.1 O'<br>4.2 Al<br>4.2.1<br>4.2.2<br>4.2.3                                                                                               | VERVIEW  _ARM PARAMETERS                                                                                                                                                                                                       |                                                 |

| 4.1 O'<br>4.2 Al<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6                                                                    | VERVIEW  _ARM PARAMETERS                                                                                                                                                                                                       |                                                 |

| 4.1 O<br>4.2 Al<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7                                                            | VERVIEW  _ARM PARAMETERS                                                                                                                                                                                                       |                                                 |

| 4.1 O'<br>4.2 Al<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6                                                                    | VERVIEW ARM PARAMETERS Alarm Title Alarm V-Flag Address Sample Rate Process Variable Address (V, WX, WY, None). PV Range Low/High (in Engr Units). PV is Bipolar (Yes/No) 20% Offset on PV (Yes/No) Square Root of PV (Yes/No) |                                                 |

| 4.1 O' 4.2 Al 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6 4.2.7 4.2.8 4.2.9                                                                       | VERVIEW  _ARM PARAMETERS                                                                                                                                                                                                       |                                                 |

| 4.1 O' 4.2 Al 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6 4.2.7 4.2.8 4.2.9 4.2.10                                                                | VERVIEW  _ARM PARAMETERS                                                                                                                                                                                                       |                                                 |

| 4.1 O' 4.2 Al 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6 4.2.7 4.2.8 4.2.9 4.2.10 4.2.11                                                         | VERVIEW ARM PARAMETERS                                                                                                                                                                                                         |                                                 |

| 4.1 Or<br>4.2 Al<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10<br>4.2.11<br>4.2.12           | VERVIEW ARM PARAMETERS                                                                                                                                                                                                         |                                                 |

| 4.1 O' 4.2 Al 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6 4.2.7 4.2.8 4.2.9 4.2.10 4.2.11 4.2.12 4.2.13                                           | VERVIEW ARM PARAMETERSAlarm TitleAlarm V-Flag AddressSample RateProcess Variable Address (V, WX, WY, None)PV Range Low/High (in Engr Units)PV is Bipolar (Yes/No)20% Offset on PV (Yes/No)                                     |                                                 |

| 4.1 O' 4.2 Al 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6 4.2.7 4.2.8 4.2.9 4.2.10 4.2.11 4.2.12 4.2.13 4.2.14                                    | VERVIEW ARM PARAMETERS                                                                                                                                                                                                         |                                                 |

| 4.1 O' 4.2 AI 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6 4.2.7 4.2.8 4.2.9 4.2.10 4.2.11 4.2.12 4.2.13 4.2.14 4.2.15                             | VERVIEW                                                                                                                                                                                                                        |                                                 |

| 4.1 O' 4.2 AI 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6 4.2.7 4.2.8 4.2.9 4.2.10 4.2.11 4.2.12 4.2.13 4.2.14 4.2.15 4.2.15 4.2.16               | VERVIEW                                                                                                                                                                                                                        |                                                 |

| 4.1 O' 4.2 AI 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6 4.2.7 4.2.8 4.2.9 4.2.10 4.2.11 4.2.12 4.2.13 4.2.14 4.2.15 4.2.16 4.2.16 4.2.17        | VERVIEW                                                                                                                                                                                                                        | 299 299 300 301 301 301 301 301 301 301 301 301 |

| 4.1 Or 4.2 Al 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6 4.2.7 4.2.8 4.2.9 4.2.10 4.2.11 4.2.12 4.2.13 4.2.14 4.2.15 4.2.16 4.2.17 4.2.18        | VERVIEW                                                                                                                                                                                                                        |                                                 |

| 4.1 O' 4.2 AI 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6 4.2.7 4.2.8 4.2.9 4.2.10 4.2.11 4.2.12 4.2.13 4.2.14 4.2.15 4.2.16 4.2.17 4.2.18 4.3 AI | VERVIEW                                                                                                                                                                                                                        |                                                 |

| CHAPTER          | 5 ANALOG (PID) LOOPS                                  | 307 |

|------------------|-------------------------------------------------------|-----|

| 5.1 O            | VERVIEW                                               | 307 |

| 5.2 LC           | OOP MODES OF OPERATION                                | 307 |

| 5.3 Lo           | OOP PARAMETERS                                        | 308 |

| 5.3.1            | Loop Title                                            |     |

| 5.3.2            | PID Algorithm (Position/Velocity)                     | 309 |

| 5.3.3            | Loop V-Flag Address (None, C, Y, V, WY)               | 310 |

| 5.3.4            | Sample Rate (in Seconds)                              | 310 |

| 5.3.5            | PV Address (None, V, WX, WY)                          |     |

| 5.3.6            | PV Range (Low/High)                                   |     |

| 5.3.7            | PV Bipolar (Yes/No)                                   |     |

| 5.3.8            | 20% Offset on PV (Yes/No)                             |     |

| 5.3.9            | Square Root of PV (Yes/No)                            |     |

| 5.3.10           | Loop Output Address (None, WY, V)                     |     |

| 5.3.11           | Output is Bipolar (Yes/No)                            |     |

| 5.3.12           | 20% Offset on Output (Yes/No)                         |     |

| 5.3.13<br>5.3.14 | Ramp/Soak for SP (Yes/No)                             |     |

| 5.3.14           | Absolute Alarm Limits (in Engr Units)                 |     |

| 5.3.16           | Remote SP (None, V, K, WX, WY, LMN)                   |     |

| 5.3.17           | Clamp Setpoint Limits Low/High (in Engr Units)        |     |

| 5.3.18           | Loop Gain                                             |     |

| 5.3.19           | Loop Reset (Reset Time in Minutes)                    |     |

| 5.3.20           | Rate (Derivative Time in Minutes)                     |     |

| 5.3.21           | Freeze Bias (Yes/No)                                  |     |

| 5.3.22           | Derivative Gain Limiting (Yes/No)                     |     |

| 5.3.23           | Limiting Coefficient                                  |     |

| 5.3.24           | Alarm Deadband (in Engr Units)                        | 314 |

| 5.3.25           | Special Calculation On (SP, PV, Output, None)         | 315 |

| 5.3.26           | Special Function                                      |     |

| 5.3.27           | Lock Setpoint, Lock Auto/Man, Lock Cascade            |     |

| 5.3.28           | Error Operation (Error Squared, Error Deadband, None) |     |

| 5.3.29           | Reverse Acting (Yes/No)                               |     |

| 5.3.30           | Monitor Deviation (Yes/No)                            |     |

| 5.3.31           | Deviation Alarm Limits (in Engr Units)                |     |

| 5.3.32           | Monitor Rate (Yes/No)                                 | 316 |

| 5.3.33           | Rate of Change Alarm Limit (in Engr Units per Minute) |     |

| 5.3.34           | Monitor Broken Xmit (Yes/No)                          |     |

|                  | OOP CONTROL FLAGS (C-FLAGS)                           |     |

| 5.5 LC           | OOP ALARM ACKNOWLEDGEMENT FLAGS                       | 318 |

| 5.6 R/           | AMP/SOAK OPERATION                                    | 319 |

| <b>CHAPTER 6</b> | MEMORY CONFIGURATION                                                                     | 321 |

|------------------|------------------------------------------------------------------------------------------|-----|

| 6.1 OVE          | ERVIEW                                                                                   | 321 |

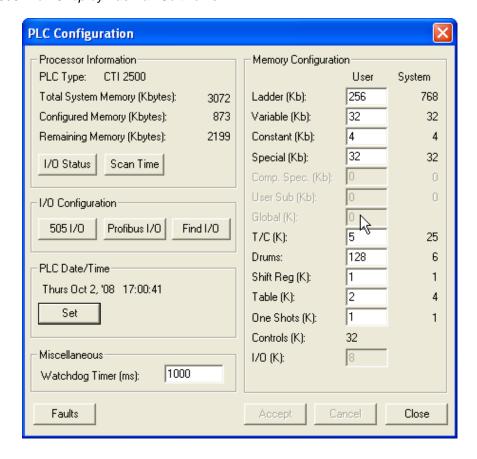

| 6.2 Mer          | MORY CONFIGURATION                                                                       | 322 |

| 6.2.1            | Ladder (L) Memory                                                                        |     |

| 6.2.2            | Variable (V) Memory                                                                      | 322 |

| 6.2.3            | Constant (K) Memory                                                                      |     |

| 6.2.4            | Special (S) Memory                                                                       |     |

| 6.2.5            | Timer/Counter (TC) Memory                                                                |     |

| 6.2.6            | Drum Memory (D) Memory                                                                   |     |

| 6.2.7<br>6.2.8   | Shift Register (SR) Memory                                                               |     |

| 6.2.9            | Table (T) Memory One Shot (OS) Memory                                                    |     |

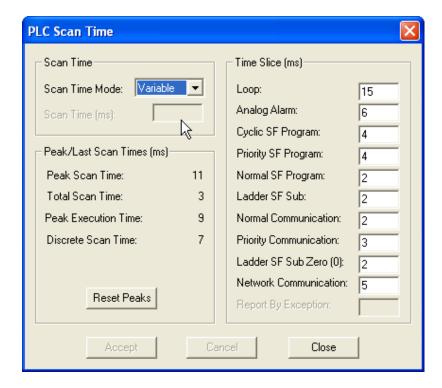

| CHAPTER 7        | SCAN CONFIGURATION                                                                       | 325 |

| 7.1 OVE          | ERVIEW                                                                                   | 325 |

| 7.2 TIM          | E SLICE CONFIGURATION                                                                    |     |

| 7.2.1            | Analog Loop Time Slice                                                                   |     |

| 7.2.2            | Analog Alarm Time Slice                                                                  |     |

| 7.2.3            | Cyclic Special Function Program Time Slice                                               |     |

| 7.2.4<br>7.2.5   | Priority Special Function Program Time Slice  Normal Special Function Program Time Slice |     |

| 7.2.5<br>7.2.6   | Ladder Special Function Subroutine Time Slice                                            |     |

| 7.2.7            | Normal Communications Time Slice                                                         |     |

| 7.2.8            | Priority Communications Time Slice                                                       |     |

| 7.2.9            | Ladder SF Subroutine 0 Time Slice                                                        |     |

| 7.2.10           | Network Communications Time Slice                                                        | 327 |

| 7.3 FAC          | CILITIES FOR ANALOG SCAN OPTIMIZATION                                                    | 327 |

| 7.3.1            | Status Word 162                                                                          | 327 |

| 7.3.2            | Program Elapsed Times                                                                    | 328 |

| APPENDIX A       | A – PLC STATUS WORDS                                                                     | 329 |

| APPENDIX I       | B – LOOP AND ALARM FLAGS                                                                 | 339 |

| LOOP V-FL        | AGS (LVF)                                                                                | 339 |

| LOOP CON         | TROL FLAGS (LCFH AND LCFL)                                                               | 340 |

|                  | FLAGS (AVF)                                                                              |     |

| ALARM CO         | NTROL FLAGS (ACFH AND ACFL)                                                              | 341 |

|                  | KNOWLEDGEMENT FLAGS (LACK AND AACK)                                                      |     |

| LIMITED PR       | ODUCT WARRANTY                                                                           | 343 |

| DEDAID DO        | LICY                                                                                     | 2/5 |

### CHAPTER 1 OVERVIEW

#### 1.1 Introduction

This manual is intended for use by individuals who are developing application programs for the CTI 2500 Series controller. Additional information about the controller, including the scan operation, is contained in a companion manual, the *CTI 2500 Installation and Operation Guide*.

The CTI 2500 is an advanced function controller that combines the features of a programmable logic controller and a loop controller. It is especially suitable for process control applications that require analog control as well as discrete control.

# 1.2 Programming Overview

The CTI 2500 controller provides several facilities for programming a control application.

- Relay Ladder Programming

- Special Function Programming

- Analog Alarms

- Analog Loops

# 1.2.1 Relay Ladder Programming

Relay Ladder Logic (RLL) is a graphical language similar to a relay diagram. It has traditionally been used for discrete control applications. The RLL language supported by the CTI 2500 is compatible with the RLL used in the Siemens SIMATIC® 505 PLC. The RLL language includes the following groups of instructions.

#### **Electro-Mechanical Replacements**

These instructions include contacts, coils, timers, counters, and drums (stepper switches).

#### Bit Manipulation

These instructions provide the capability of reading, setting, and clearing bits as well as performing logical AND / OR operations.

#### **BCD Conversions**

The BCD instructions allow you to convert numbers between binary and binary coded decimal formats.

#### **Word Move Instructions**

Word Move instructions copy bits of a word values from source location(s) to a destination, which may be another memory type or another address within the same memory type. You can also copy selected bits between a word data type and a discrete Boolean data type.

### Math

The Math instructions perform traditional integer mathematical calculations, including addition, subtraction, multiplication, division and square root. You can also perform compare operations.

1

#### **Table Instructions**

The table instructions provide a means to manipulate array data. You can move data in and out of a table, perform table searches, and perform bit level comparisons between two tables.

#### **Real-time Clock Instructions**

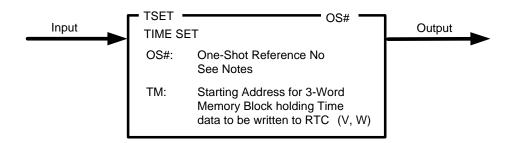

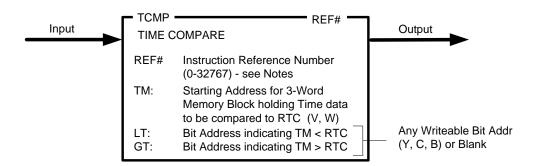

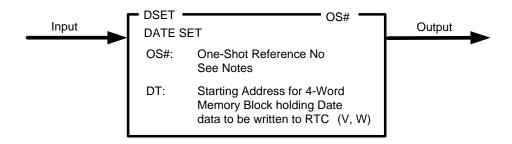

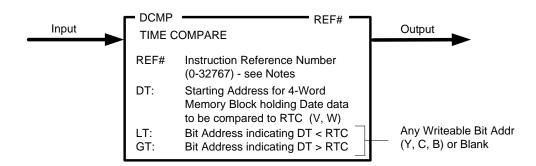

The clock instructions read and set the Time and Date for the Real-time Clock in RLL.

#### **Subroutine Instructions**

The subroutine instructions allow you to create and call RLL subroutines. They also include the ability to call Special Function programs and subroutines.

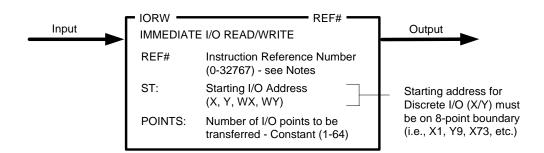

#### Immediate I/O instructions

The Immediate I/O instructions read or write to the physical I/O during RLL execution rather than waiting for the normal I/O update to take place later in the controller scan.

#### Miscellaneous

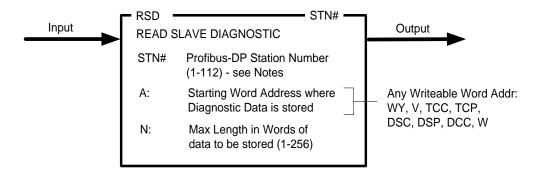

The RLL also contains instructions that allow you to turn on an output for a single scan (one-shot), read diagnostic data from Profibus, and execute a PID loop on demand.

# 1.2.2 Special Function Programs and Subroutines

Special Function (SF) programs and subroutines provide a statement-oriented procedural programming language. Using the Special Function instructions, you can derive solutions that cannot be done in RLL or would require complex RLL programming.

SF programs can be called from an RLL program or from analog loop or alarm tasks. SF subroutines can be called from RLL, SF programs, or other SF subroutines. SF programs and SF subroutines use a common instruction set.

Special Function Program instructions include the following groups:

#### **Data Conversion**

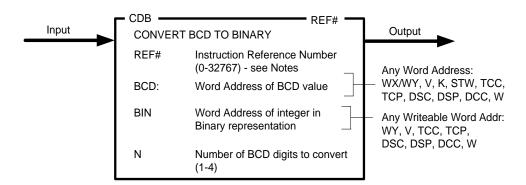

These instructions provide the capability to scale values and to convert between BCD and binary format.

#### Math

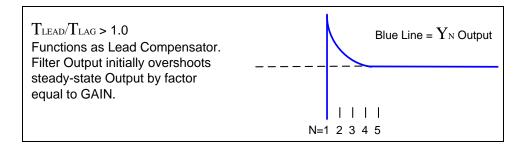

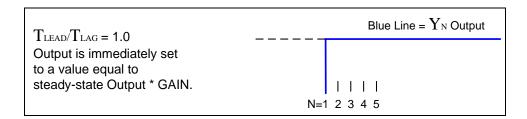

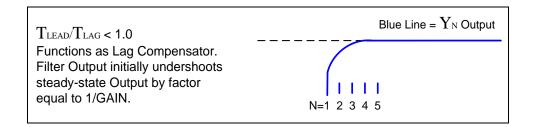

Math instructions support both integer and real numbers. Operators include standard math functions (add, subtract, multiply, divide, exponentiation, comparison, and bit operations) as well as a unique LEAD/LAG function that can be used with cyclic applications.

#### **Program Flow**

These instructions alter the order in which instructions are executed. They include the ability to call subroutines, to branch to a label, and to implement conditional branching (If, Then, Else).

#### **Data Manipulation**

These instructions provide the ability to search tables, pack and unpack data, and to perform various shift register operations.

# 1.2.3 Analog Alarms

Analog Alarms are parameter-driven functions that allow you to monitor the Process Variable (PV). Each alarm block allows you to configure up to four absolute-value alarms and two sets of alarms that monitor the deviation of PV from the Setpoint. In addition, you can monitor the rate-of change of the Process Variable and detect a broken transmitter. An analog alarm may call a special function program to perform additional calculations. The number of analog alarm functions supported is model dependent. See the *CTI 2500 Installation and Operation Guide* for CTI 2500 Series model capabilities.

# 1.2.4 Analog Loops

The Analog Loop function supports both VELOCITY and POSITION PID (Proportional-Integral-Derivative) algorithms. Analog Loops are used to control analog processes by varying the loop output so that the output of the process (PROCESS VARIABLE) matches a target value (SETPOINT).

The operation of a particular loop is established by parameters entered by the user. In addition to executing the control loop, the loop task also provides the same alarm monitoring capability as the Analog Alarm task described in the next section.

The SETPOINT can also be automatically varied using a RAMP/SOAK Table. The RAMP/SOAK Table allows you to program a change in the SETPOINT over time (RAMP) and followed by a period that the SETPOINT will remain the same (SOAK). Using a series of ramp/soak steps, you can control most batch processes.

Loops are typically executed on a cyclic basis, independent of the user RLL or SF program logic. Some models of the CTI 2500 also support the capability of calling a PID loop from the RLL.

Loops may be cascaded, where the output of one loop becomes the input for the next loop. A loop may call a Special Function program to perform additional calculations. The number of loops supported is model dependent. See the *CTI 2500 Installation and Operation Guide* for CTI 2500 Series model capabilities.

# 1.3 Controller Data Types

The following data types are accessible from the user program. The value within a data element is addressed by specifying the data type and a location number. For example discrete input 1 is referenced as X1.

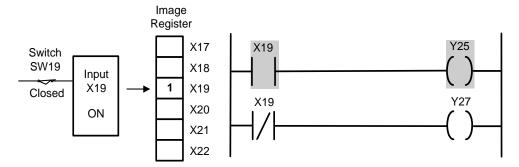

### I/O Register Data

The I/O register contains the data obtained from the process (inputs) and data used to control the process (outputs). When the I/O is configured, this data is associated with input and output modules contained in the local base, remote bases, and slaves attached to the Profibus network. There is an I/O register representing discrete inputs and outputs and an I/O register representing Word Inputs and Outputs. The table below describes the contents:

| Mnemonic | Data Type       | Data Format   | Access         |

|----------|-----------------|---------------|----------------|

| Χ        | Discrete Input  | Bit           | Read Only      |

| Υ        | Discrete Output | Bit           | Read and Write |

| WX       | Word Input      | Word (16 bit) | Read Only      |

| WY       | Word Output     | Word (16 bit) | Read and Write |

Inputs and Outputs share the same I/O register location. Therefore X1 and Y1 are the same data point. Similarly WX1 and WY1 are the same.

#### **Control Relay Data**

A Control Relay is an internal discrete value that can be written and read by user logic. It is not associated with any I/O point. The number of control relays supported depends on the controller model. See the *CTI 2500 Installation and Operation Guide* for CTI 2500 Series model capabilities.

Control relays may be retentive or non- retentive. Retentive control relays maintain their value when AC power is removed, assuming the controller battery is good. Whether a particular control relay is retentive or not depends on the control relay address. See the table below.

| Non-Retentive   | Retentive      |

|-----------------|----------------|

| C1 – C768       | C769 – C1024   |

| C1025 – C1792   | C1793 – C2048  |

| C2049 – C2816   | C2817 - C3072  |

| C3073 – C3840   | C3841 – C4096  |

| C4097 – C4864   | C4865 – C5120  |

| C5121 – C5888   | C5889 – C6144  |

| C6145 – C6912   | C6913 – C7168  |

| C7169 – C7936   | C7937 – C10240 |

| C10241 – C56320 |                |

### **Variable Memory Data**

Variable Memory (V Memory) is a collection of 16 bit words. The number of words available depends on the controller user configuration and the available user memory, which varies with the controller model. V memory can be read and written by the user program.

#### **Constant Memory Data**

Constant Memory (K Memory) is a collection of 16 bit words. The number of words available depends on the controller user configuration and the available user memory, which varies with the controller model. K memory can be read but not written by the user program. It can be modified by other sources, such as programming software.

#### **Status Word Memory Data**

Status Word Memory (STW) is a collection of 16 bit words user to communicate the status of the controller, the user program, and the associated I/O to the user program. Status cannot be modified by the user program; however some status words can be modified by programming software. See Appendix A for a list of the status words used with the CTI 2500 controller.

#### **Timer Counter Memory Data**

The Timer/Counter memory contains two values for each element as indicated below.

| Mnemonic | Data Type             | Data Format   | Access           |

|----------|-----------------------|---------------|------------------|

| TCP      | Timer Counter Preset  | Word (16 bit) | Read/Write       |

| TCC      | Timer Counter Current | Word (16 Bit) | Read/Write (RLL) |

|          |                       |               | Read Only (SF)   |

#### Note:

Changes to TCP do not modify the value save in the RLL program. TCP values modified by logic or HMI will be overwritten by the original stored value if the program is reloaded, the network containing the Timer/Counter instruction is edited, or a Complete Restart is executed.

#### **Drum Memory Data**

The Drum memory contains four values for each drum as indicated below

| Mnemonic | Data Type          | Data Format   | Access           |

|----------|--------------------|---------------|------------------|

| DSP      | Drum Step Preset   | Word (16 bit) | Read/Write       |

| DSC      | Drum Step Current  | Word (16 Bit) | Read/Write       |

| DCP      | Drum Count Preset  | Word (16 Bit) | Read/Write       |

| DCC      | Drum Count Current | Word (16 Bit) | Read/Write (RLL) |

|          |                    |               | Read Only (SF)   |

#### Note:

Changes to DSP and DCP do not modify the RLL program. If the program is reloaded, a network containing a drum instruction is edited, or a Complete Restart is executed, modified DSP and DCP values will be replaced with the values stored in the RLL program.

# 1.4 Data Representation

Data is represented in the CTI 2500 controller as bits, bytes, words, and double words.

Bit A single binary digit that has either On (1) or OFF (0) state. Bit locations are referenced by direct address in discrete memory areas (i.e., X32 or C86) or bit number in word memory areas (i.e., V52.3, K2.14, WY6.1, or STW1.16)

#### Note:

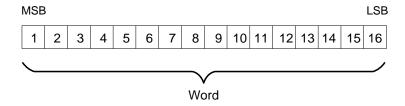

Bit assignments within words are numbered left to right so that Bit 1 is the MSB and Bit 16 is the LSB.

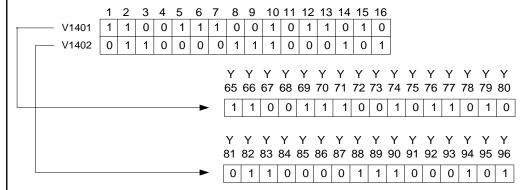

Bits within words are numbered 1-16 from left to right so that Bit 1 references the MSB and Bit 16 references the LSB as shown below.

Byte A byte consists of 8 contiguous bits used to represent a maximum unsigned value of 255. Bytes are referenced only as "Most Significant Byte" (Bits 1-8) and "Least Significant Byte" (Bits 9-16). Only one RLL instruction (Move Element – MOVE) references the byte data type directly.

**Word** A word consists of 16 bits. The word may be used to store signed integers, unsigned integers, binary coded decimal data, or a field of flag bits.

- Signed integers are stored in the two's complement format, with the sign bit in the most significant bit. When the sign bit is 0 the number is positive; when the sign bit is set to 1, the number is negative. A signed integer can contain values ranging from 32,768 to +32,767.

- Unsigned integers make use of the high bit to represent a positive number. Consequently, the value stored can range from 0 to 65, 535.

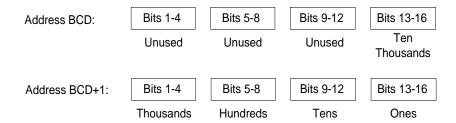

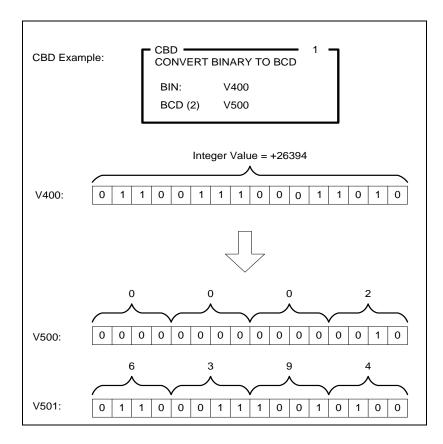

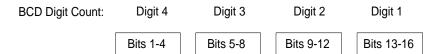

- BCD data is stored by assigning 4 bits to represent a decimal digit. As a result, one 16 bit word using BCD can hold 4 decimal digits. For example, a decimal value of 2569 would be represented as shown below.

| 2 |   |   |   | 5 |   |   | 6 |   |   | 9 |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

Hexadecimal (Hex) is simply an alternative "programmer friendly" way of representing binary data. Even though the data format is very similar to BCD, hexadecimal and BCD values are not equivalent. **Double Words** consist of two consecutive words used to contain long integers, Real numbers, and address data. Although double words are stored internally as 32 bit entities, they are addressed as two consecutive memory locations.

| MSB  |                       | LSB_ | MSB                         | LSB |

|------|-----------------------|------|-----------------------------|-----|

| V100 | Most Significant Word |      | V101 Least Significant Word |     |

|      |                       |      |                             |     |

- LONG INTEGERS are stored in the two's complement format.

Long integer values can range from -2,147,483,628 to +2,147,483,647

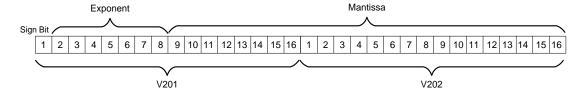

- REAL NUMBERS are stored in single-precision floating point format that complies with the ISEE Standard 754-1985 standard. This format provides 6 significant digits of resolution and supports numbers in the range of ±3.4028x10<sup>38</sup> (displayed as 3.4028E38). The following figure shows the data format for a real number addressed as (V201.).

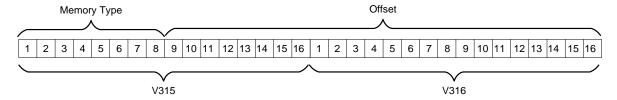

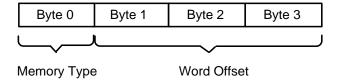

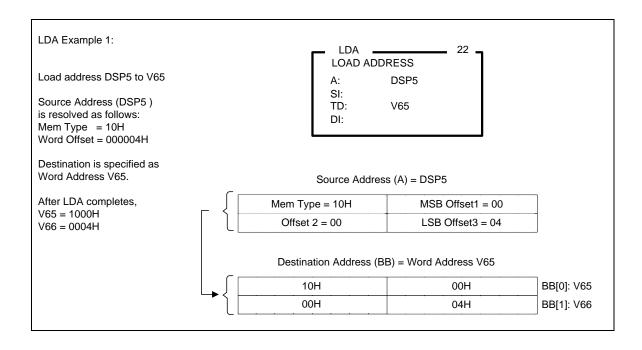

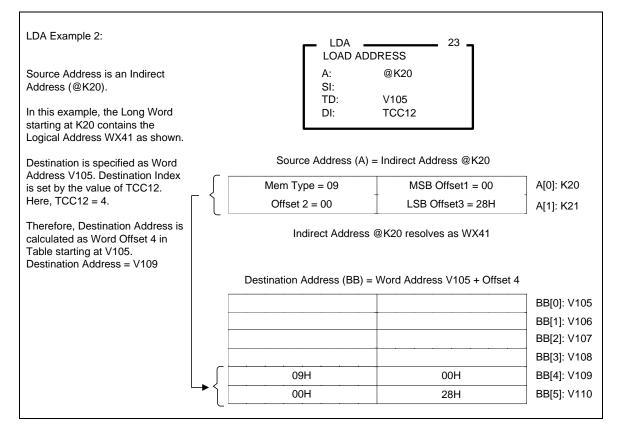

LOGICAL ADDRESS data, used by some instructions such as LDA, are stored in a special format that contains the memory type code and the address offset. The following figure shows the data format for a logical address stored in V315-V316.

#### **Memory Type codes (Hex)**

| V = 01   | DSP | = 10 |

|----------|-----|------|

| K = 02   | DSC | = 11 |

| WX = 09  | DCP | = 12 |

| WY = 0A  | DCC | = 1B |

| TCP = 0E | STW | = 1A |

| TCC = 0F |     |      |

#### 1.5 Run-Time RLL Edits

The CTI 2500 Series controller allows you to edit the RLL program while the process continues to run. While this capability provides significant benefits in some process control applications, it must be approached with care.

#### **WARNING**

Use extreme care when performing run-time edits. Incorrect changes may cause the process to fail and could result in equipment damage and/or death or serious injury to personnel.

Carefully plan any run-time edits to an active process. Avoid doing run-time edits to an active process if possible.

As the name implies, run-time edits allows changes to be made to the RLL program while the controller is in RUN mode. When you enter the first program change, the controller automatically enters a special EDIT mode. In EDIT mode, the process continues to be controlled by the original RLL program as it existed prior to entering the change. When you request a return to RUN mode after making all changes, the controller scan is extended while the new version of the program is compiled. Upon a successful compile of the new version, controller transitions to RUN mode and the process resumes with the new version in control.

#### **WARNING**

It is possible to enter program changes that will not compile and execute. If the new program will not compile successfully, the controller will enter PROGRAM mode with all outputs frozen at their last state. This could cause unpredictable operation resulting in equipment damage and/or death or serious injury to personnel. It is your responsibility to provide for safe recovery should this condition occur.

Always use the SYNTAX check function to validate all program changes before setting the controller to RUN mode.

# 1.5.1 Syntax Checking

After all required modifications are complete, you should request a syntax check to verify that the changes compile correctly before attempting to go to RUN mode. If errors are detected by syntax check, you can correct these errors and then re-execute the syntax check. This process can be repeated until the syntax check is successful, at which time you can then set the controller to the RUN mode. For Workshop users, the syntax check function can be accessed under the *Diagnostics* menu item. TISOFT users can access the function under *Auxiliary Functions (F6)*

# 1.5.2 Potential Sources of Run-Time Edit Compile Errors

Following are some conditions that will cause the RLL compile to fail, resulting in the controller being placed in PROGRAM mode with outputs frozen. Always request a syntax check before attempting to go to RUN mode.

#### SKP Instruction without a Corresponding LBL

There must be a LBL statement associated with each SKP instruction and it must occur in the same program segment (SBR or TASK) as the SKP instruction.

### SBR instruction without a terminating RTN

A subroutine must be terminated by an **unconditional RTN** instruction.

#### GTS, PGTS or PGTSZ without corresponding SBR

The subroutine referenced by a GTS, PGTS, or PGTSZ instruction must be defined before it can be referenced.

#### Use of unsupported features

Your RLL program must not use an instruction that is not supported by the firmware release installed in your controller or reference undefined or unconfigured data elements. This condition may not be detected by all versions of all programming software tools.

#### **Exceeding L Memory**

When you modify or add networks to an RLL program using the run-time edit function, it is possible for the edited program to exceed the amount of L-Memory that has been configured. If the configured L-Memory capacity is exceeded, one or more networks at the end of the program will be deleted when the new program is compiled. Workshop and TISOFT provide a warning of this condition prior to accepting the editing change. However, if you proceed with accepting the change and then select RUN, it is possible that the program will fail to compile or the program may execute incorrectly. Prior to making a run-time change you can determine L memory status by selecting the *PLC Utilities/PLC Status* menu item in Workshop or *Auxiliary Functions (AUX 28)* in TISOFT.

#### 1.5.3 Additional Considerations

When you edit an existing network, Workshop or TISOFT will delete the existing network and then insert the edited network in its place. If the original network contains an instruction with retained state information and this instruction remains in the network after the edit, you may experience unexpected results when transferring to RUN mode. These unexpected results occur due to initialization of the state information for the "retained state" instruction.

For example, an existing network contains a One-Shot contact that passes power flow for one scan when detecting an OFF-to-ON input transition. If the One-Shot input condition has been TRUE for more than one scan, the output coil is turned OFF and will remain OFF until the input state goes FALSE and back TRUE. However, if the network is edited at this point, the "retained state" of the One-Shot will be lost and re-initialized when the program is compiled so that the output coil will turn ON for one scan immediately following the transfer to RUN mode.

#### **WARNING**

Take extreme care when performing a run-time edit on an existing network that contains one or more "retained state" instructions. When returning to RUN mode following the edit, these instructions are re-initialized during the program compilation. This may cause the network output coil(s) to temporarily change state.

You may experience unexpected results that could result in damage to equipment and/or death or serious injury to personnel. If you must edit a network containing one of these instructions, you must consider the effect upon the process caused by this initialization and ensure that the process state can safely handle this effect.

The instructions with retained state information are shown in the following table.

| Operati                 | on of Retained-State Instructions in Networks affected by Run-Time Edits                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

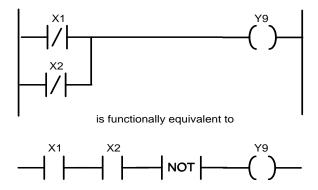

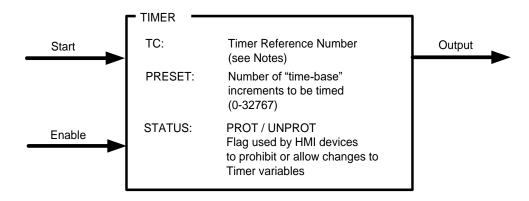

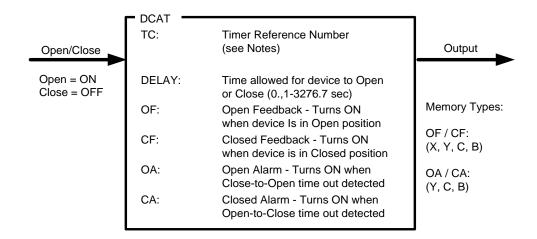

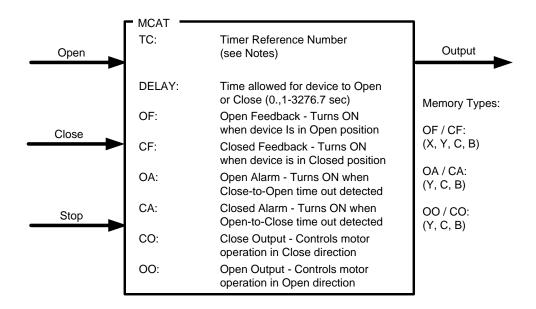

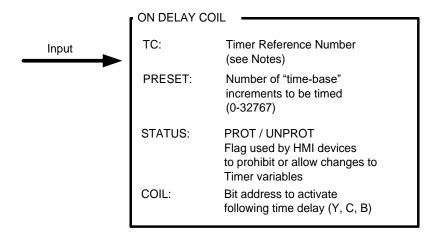

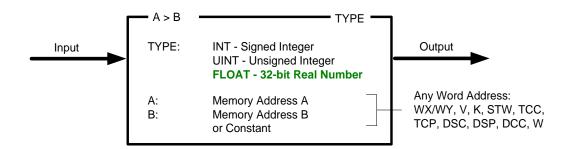

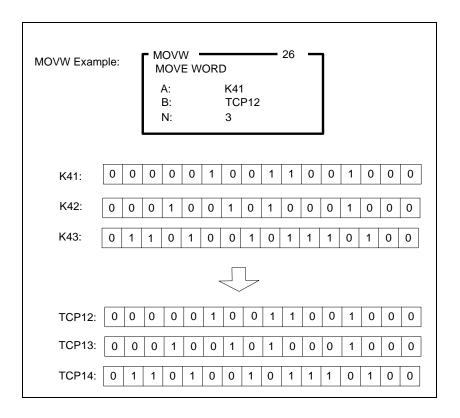

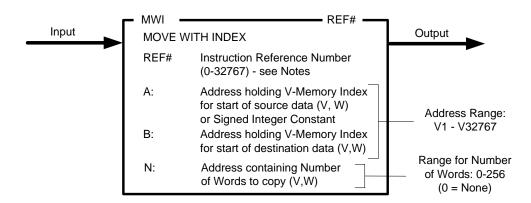

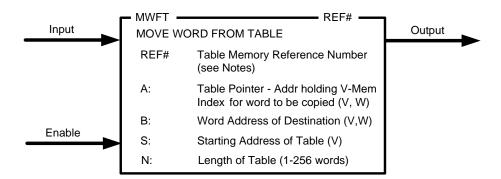

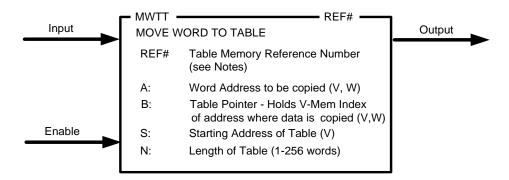

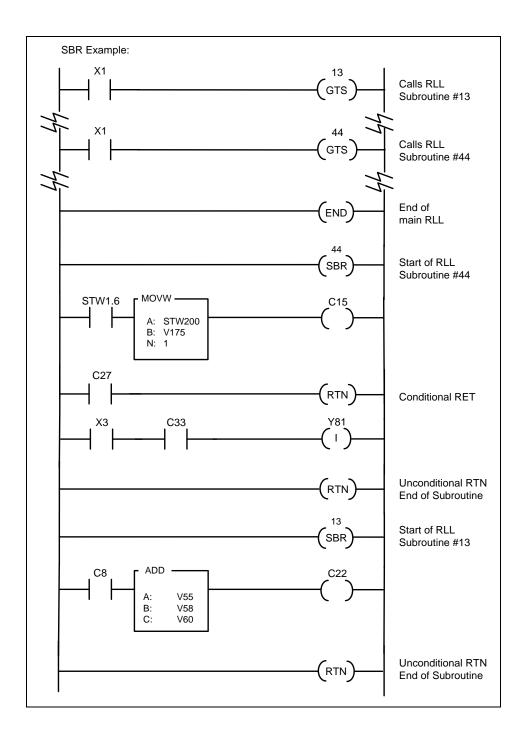

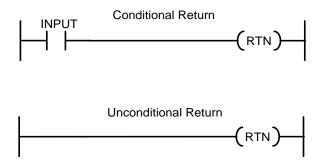

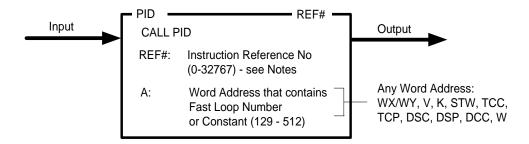

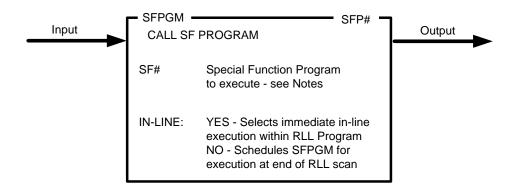

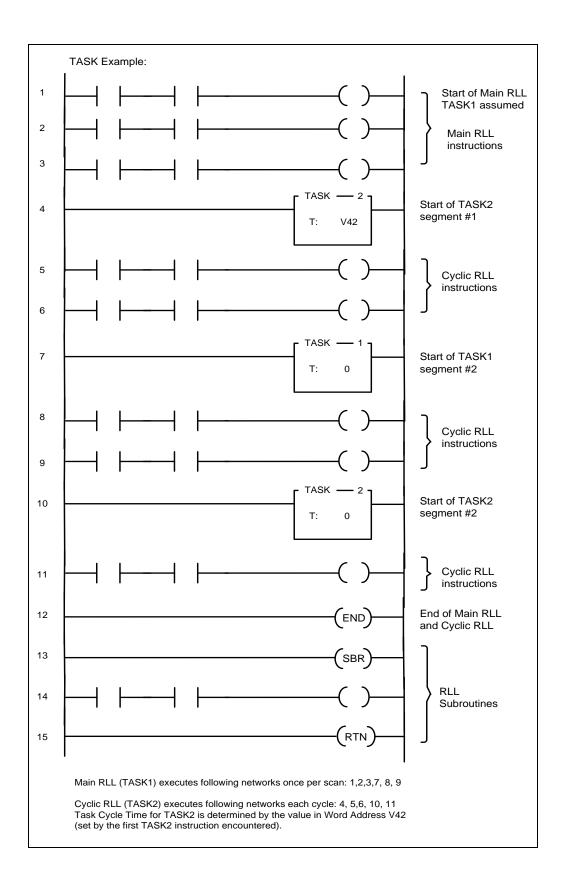

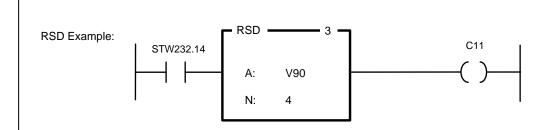

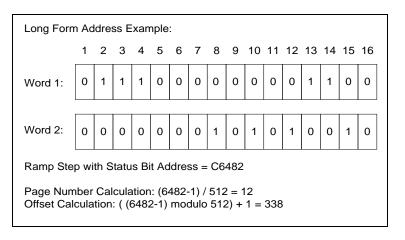

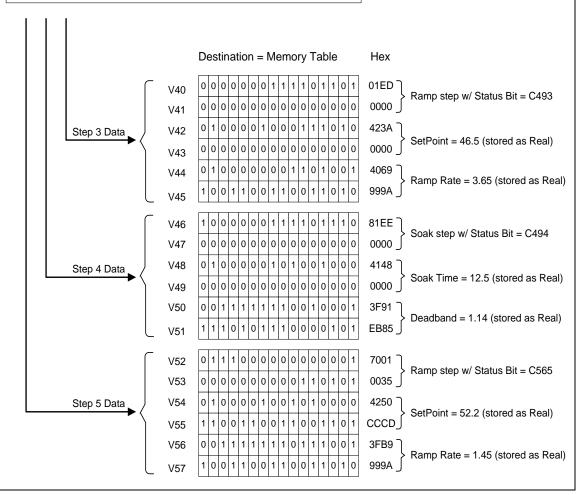

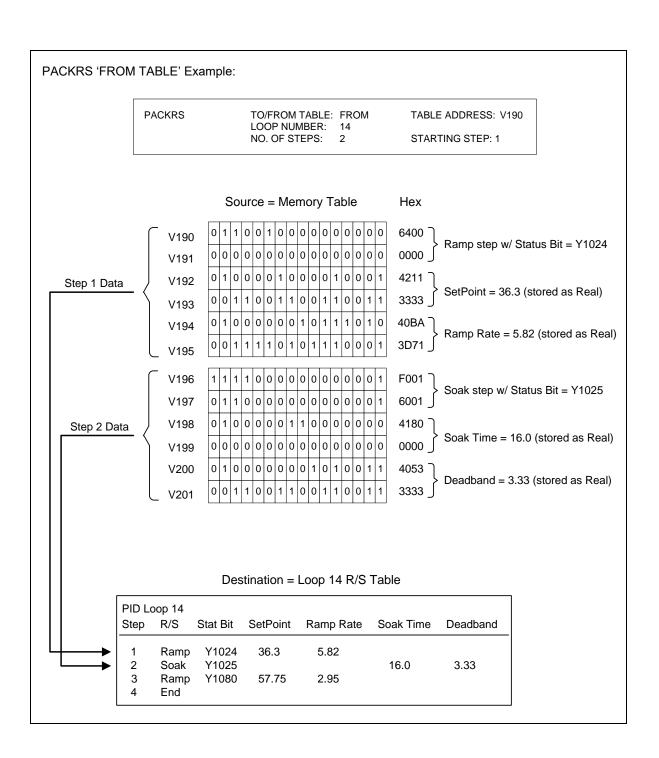

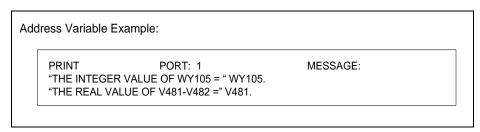

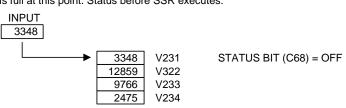

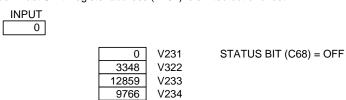

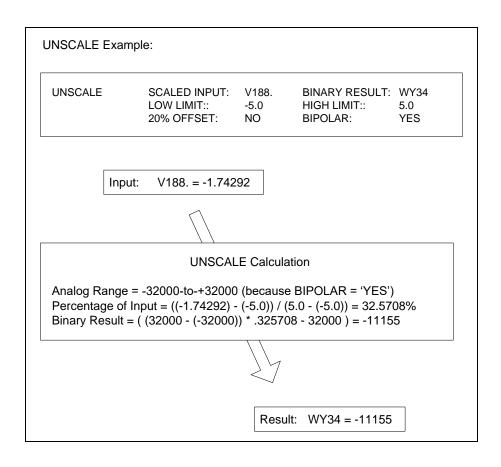

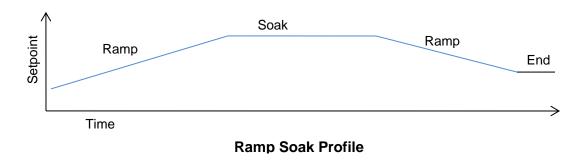

| Instruction             | Initial Condition After Run-Time Edit                                                                                                                                                                                                                                                                                                                                                                                                              |